1-1. Gap fill

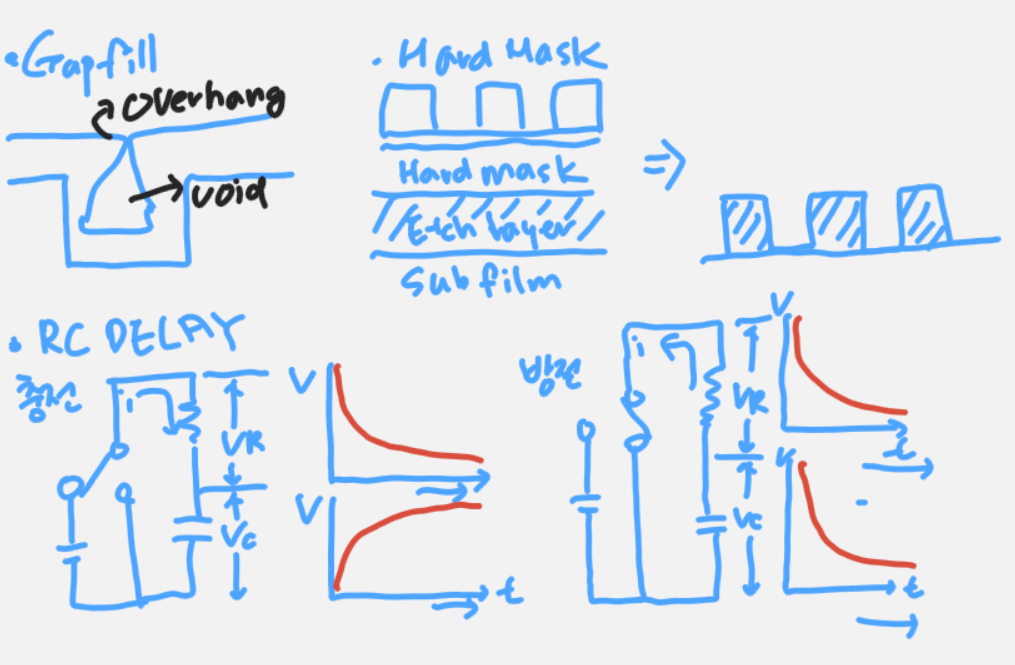

배선과 배선 사이 절연막으로 채울 때 VOID가 없어야 합니다. Void 발생 시 후속 공정 진행 시 문제를 야기할 수 있습니다. 보통 이러한 문제의 원인은 패턴 막질 사이 절연막을 Gap fill을 할 때 상부 방향과 측면 방향에서의 증착 속도가 일정하지 않아 Overhang이 만들어지면서 내부 빈 공간을 만들고 증착이 완료되면서 만들어집니다.

SiO2 공정에 SiH4 TEOS가 우수한 Step Coverage를 나타내어 Precursor TEOS가 SiH4보다 Sticking Coefficient가 낮아 우수한 특성을 지니고 있습니다.

Precursor란 무엇일까요? 전구체라고도 하며 반도체 공정 진행 시 반응기 내에 여러 종류의 반응 기체를 유입시켜 화학반응을 진행함으로써 원하는 물질의 박막을 웨이퍼 상에 증착하는 데 사용되는 유기금속 화합물입니다.

Sticking Coefficient란? 반응 가스가 외부로부터 주입되어 표면에 얼마나 움직이지 않고 붙어 있는지를 나타내는 지표입니다.

미세 공정의 경우 채워지는 Aspect Ratio가 높아짐에 따라서 이를 극복하기 위한 공정 개발이 지속되고 있습니다.

1-2. HARD MASK

하드마스크란 무엇일까요? Patterning 공정에 필요한 film으로 다른 2개의 박막 필름을 제거하는 속도 차이를 이용해 Etch 하는 방법을 말합니다. 보통은 남기고자 하는 FILM 위로 PR을 남기고 Etch를 하는 방법이나 선폭이 작아져서 이 방법이 한계에 다다르면서 Hardmask를 이용한 Etch를 합니다. 초기에는 Oxide Etch 진행 시 선택비 차이를 이용한 Nitride Film이 사용되었지만 이후 선폭이 작아져 대부분 공정에서 Hard Mask가 필요하게 되면서 PR과 비슷한 Patterning 이 완성된 후 쉽게 O2 Ashing이 되어 처리 가능한 Carbon film이 사용됩니다.

1-3. Low-K 절연막

반도체는 Shrink 됨에 따라 RC Delay로 인한 동작 속도와 손실이 발생합니다. Metal과 Metal 사이 절연막의 물질이 유전율이 클 경우 실제 동작에 따른 Cap이 존재하여 실제 배선의 속도에 영향을 주어 속도 저하를 유발합니다.

유전율(permittivity) : 전매 상수란 뜻으로 전하 사이에 전기장이 작용할 때 그 사이 매질이 전기장에 미치는 영향을 나타내는 물리적 단위입니다. 매질이 저장할 수 있는 전하량으로 볼 수 있습니다. 즉 부도체의 전기적인 특성을 나타내는 중요한 특성 값입니다.

RC Delay란? 저항 R과 케페시턴스 C 값을 곱한 값으로 전기 신호 전달 속도 지연을 의미합니다.

전자 기기는 디지털 신호를 사용하므로 0과 1을 인식할 수 있습니다. 충전(1), 방전(0)이 중요하지 그 사이 시간은 필요 없습니다.

RC Delay를 낮추기 위해서는 1) 저항을 낮추는 방법 2) 케페시턴스를 낮추는 방법을 사용합니다.

저항이란 아래와 같이 길이에 비례 면적에 반비례하는데 배선이 얇아질수록 배선의 저항은 점점 커지게 됩니다. 따라서 저항을 낮추려면 비저항 값을 최대한 적은 재료로 사용해야 합니다. 예전에는 Al을 사용했다면 최근에는 Cu로 재료 변경을 하였습니다.

저항(R) = 비저항(p) × l(길이)/A(면적)

두 번째로 캐패시턴스 관점으로 보면 이것은 유전율이 비례, 면적에 비례, 두께에 반비례합니다.

게이트 산화막에서는 어느 정도의 캐패시턴스 값을 갖고 있어야 하는데 갖은 전압에서 쉽게 채널을 형성하기 위해 두께가 얇아지기 시작하고 Oxide 두께가 너무 얇아지면 전자의 터널링 effect가 발생하므로 두께는 일정 수준 유지하고 높은 유전율 (High k) 물질을 사용합니다.

반대로 배선에서는 RC Delay 때문에 Metal line을 둘러싼 절연체의 커패시턴스가 작아야 합니다. 이때 낮은 유전율을 가지는 low -k 물질을 사용합니다.

절연막 SiO2 FILM막이 유전율 수준으로 오랫동안 사용되었지만 이후 유전율(K) 값을 낮춰가기 위해 최근에는 Low-K 기술이 적용되었습니다.

유전율이 낮아질수록 수분 흡수와 경도(Hardness)가 취약해지고 열에 의한 Stress 변화 폭 차이가 크게 나타나서 이에 대한 최적화 공정 방안이 필요합니다.

'반도체 기술' 카테고리의 다른 글

| Diff 공정 - Furnace장비 (10) | 2023.02.13 |

|---|---|

| DIFF 주요 설비 - Furnance (15) | 2023.02.12 |

| MOSFET에 대한 이해 (6) | 2023.02.10 |

| ICP ( Inductively Coupled Plasma ) 전기적 특성 (8) | 2023.02.09 |

| NET DIE (1) | 2023.02.08 |